# Introduction to CMOS VLSI Design Lecture 5: Logical Effort David Harris Harvey Mudd College Spring 2004

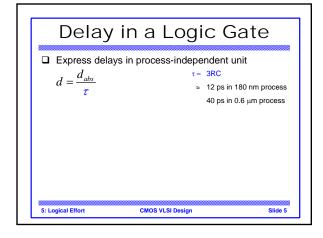

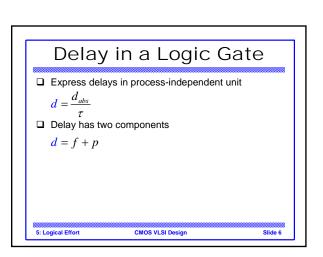

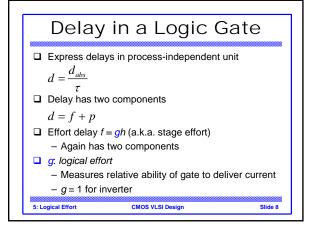

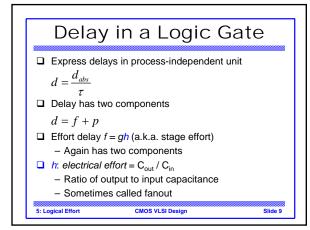

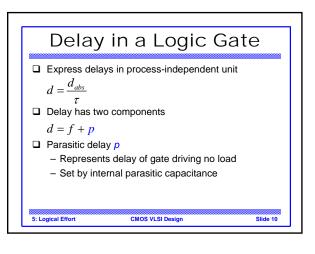

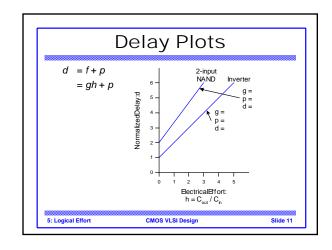

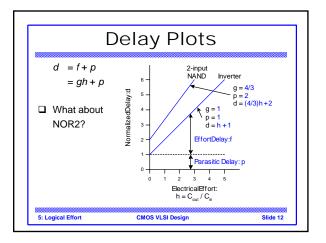

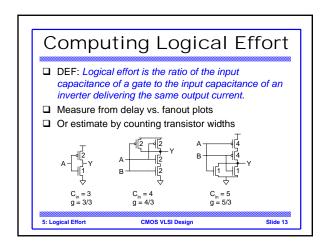

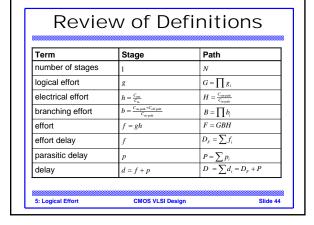

### Delay in a Logic Gate Express delays in process-independent unit $d = \frac{d_{abs}}{\tau}$ Delay has two components d = f + pEffort delay f = gh (a.k.a. stage effort) Again has two components

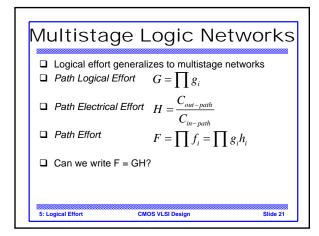

### Multistage Delays

□ Path Effort Delay

$$D_F = \sum f_i$$

$\square$  Path Parasitic Delay  $P = \sum_{i} p_{i}$

$$P = \sum p_i$$

□ Path Delay

$$D = \sum d_i = D_F + P$$

5: Logical Effort

CMOS VLSI Design

### **Designing Fast Circuits**

$$D = \sum d_i = D_F + P$$

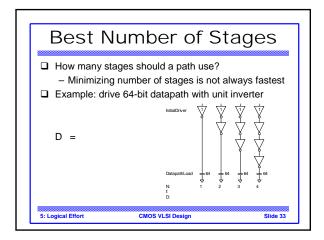

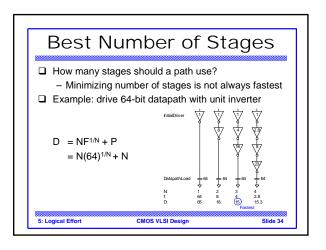

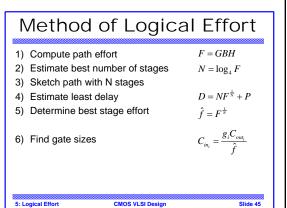

☐ Delay is smallest when each stage bears same effort

$$\hat{f}=g_ih_i=F^{\frac{1}{N}}$$

☐ Thus minimum delay of N stage path is

$$D = NF^{\frac{1}{N}} + P$$

- ☐ This is a key result of logical effort

- Find fastest possible delay

- Doesn't require calculating gate sizes

CMOS VLSI Design

Slide 26

### **Gate Sizes**

☐ How wide should the gates be for least delay?

$$\hat{f} = gh = g \frac{C_{out}}{C_{in}}$$

$$\Rightarrow C_{in_i} = \frac{g_i C_{out_i}}{\hat{f}}$$

- ☐ Working backward, apply capacitance transformation to find input capacitance of each gate given load it drives.

- ☐ Check work by verifying input cap spec is met.

5: Logical Effort

CMOS VLSI Design

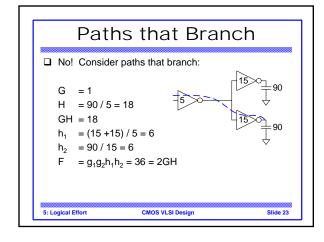

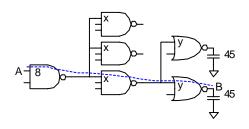

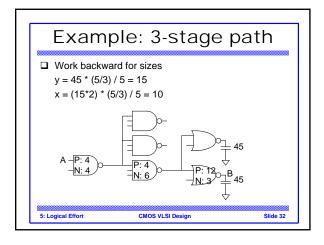

### Example: 3-stage path

☐ Select gate sizes x and y for least delay from A to B

CMOS VLSI Design

### Example: 3-stage path

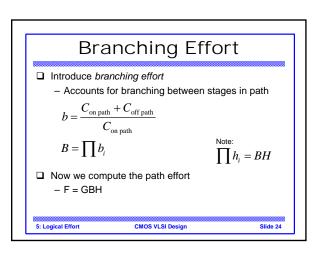

Logical Effort

**Electrical Effort** H=

B= **Branching Effort** Path Effort

$\hat{f} =$ Best Stage Effort Parasitic Delay

Delay

CMOS VLSI Design 5: Logical Effort

### Example: 3-stage path

G = (4/3)\*(5/3)\*(5/3) = 100/27Logical Effort

**Electrical Effort** H = 45/8B = 3 \* 2 = 6 **Branching Effort** F = GBH = 125 Path Effort  $\hat{f} = \sqrt[3]{F} = 5$ Best Stage Effort

Parasitic Delay P = 2 + 3 + 2 = 7 Delay D = 3\*5 + 7 = 22 = 4.4 FO4

5: Logical Effort

CMOS VLSI Design

###

###

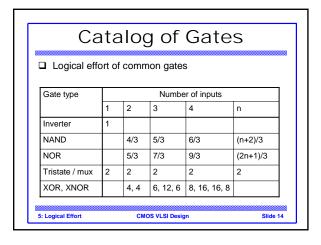

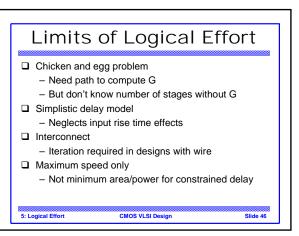

# Summary □ Logical effort is useful for thinking of delay in circuits - Numeric logical effort characterizes gates - NANDs are faster than NORs in CMOS - Paths are fastest when effort delays are ~4 - Path delay is weakly sensitive to stages, sizes - But using fewer stages doesn't mean faster paths - Delay of path is about log₄F FO4 inverter delays - Inverters and NAND2 best for driving large caps □ Provides language for discussing fast circuits - But requires practice to master